Deeds is free Digital Logic Simulator to simulate the digital circuit. Digital Logic Simulator lets you draw the digital circuit using predefined digital components and simulate them.

Along with the simulation feature Deeds also offers you to Generate VHDL Code using the created digital design. Also, Deeds lets you carry out to test the digital circuit in FPGA simulation.

I have tested Deeds in Windows 7. I designed a Digital Circuit and then I simulated the circuit, generated VHDL code for it and carried out the circuit test in FPGA simulator. I have posted a simulation clip below, of the Digital Circuit I designed using Deeds Digital Logic Simulator.

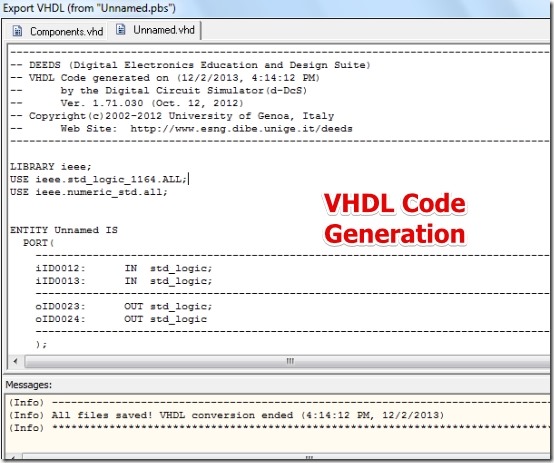

Along with the simulation you can see below the part of the VHDL code that I generated for the Digital circuit.

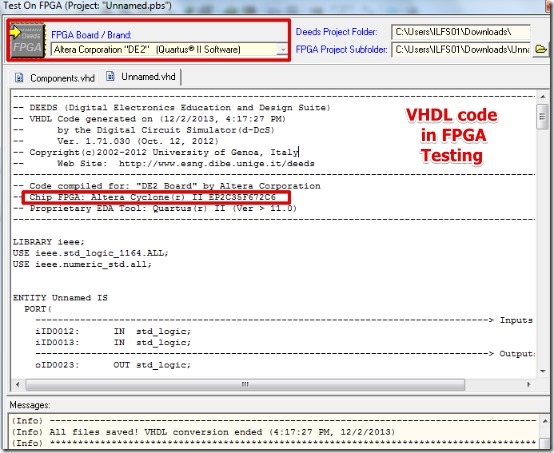

Also, the FPGA VHDL code can be generated in FPGA simulation in Deeds Digital Logic Simulator. See below to get an idea.

Note that I have posted only part of the codes not the complete Code.

Also, note that Deeds also offers simulation for Micro Computers and Finite State Machine models. I have not reviewed them. I have reviewed the Digital Logic Simulator part of Deeds in the article. You can try out other features also.

Working with Deeds Digital Logic Simulator:

It is not at all tough to design the circuit and then simulate it, along with the VHDL Code Generation and testing in FPGA simulation.

First in order to design the circuit you have to launch the Deeds Digital Logic Simulator from Start –> All programs – > Deeds – > Digital Circuit

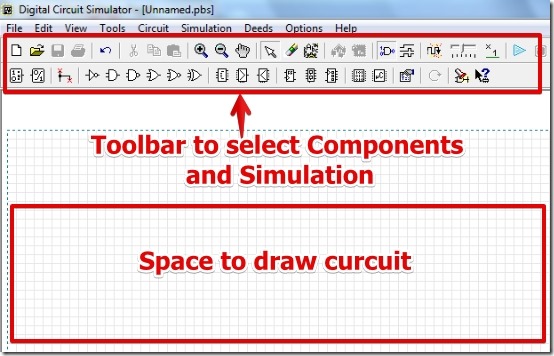

After you run the Deeds Digital Logic Simulator you will have the user interface as shown below.

The user interface is simple and you can simply drag and drop the components from the menu option on the top in order to place the components for the circuit.

You can select wire, input, output, clock from the menu options. For the components Deeds offers:

- Logic Gates (Dual and Multiple Inputs).

- Encoders and Decoders.

- Multiplexers.

- Demultiplexers.

- Flip Flops.

- Registers.

- Counters.

- Micro Computer.

- Finite State Machine.

After designing the circuit from the components, Deeds offers:

- Simulation of the circuit: In order to simulate the circuit, just draw the circuit, then save the circuit and select Simulation – > Start Simulation. You can edit the inputs from 1 or 0 using the inputs as shown in the simulation above.

- Generation of VHDL Code: In order to generate the VHDL code you have to design the circuit. Then select File – > Export in VHDL. You will have a code in VHDL generated for you.

- Testing the circuit in FPGA simulation: In order to test the circuit you have to select File – > Test on FPGA. Select the board for simulation and then select parameters such as input and output switch. After selecting the parameters click on Generate Project. You will have a VHDL code generated for you for the Board selected. The result will be stored on the folder where the VHDL files are stored. You need not worry about the location as you will be prompted to see the location of the result folder.

Features of Deeds:

- Nice collection of the components.

- Easy to use.

- Option to simulate the circuit.

- Zoom using mouse wheel.

- Option to cut, copy, delete, and pan the components.

- VHDL Code generation.

- FPGA code Simulation.

- Different boards offered for FPGA simulation.

- Option to add text to the drawing.

You might also like similar software Logisim and CircuitMod.

Conclusion:

Deeds Digital Logic Simulator is a great free tool for designing and simulating the Digital Logic circuits. What I really liked is the ease of use and the simulation part. The option to create the VHDL code along with FPGA simulation is also cool. Based on cool features and efficient work I would recommend you to try it out.